Eletrônica abaixo do nanômetro: Primeiros transistores estão prontos

Redação do Site Inovação Tecnológica - 04/07/2024

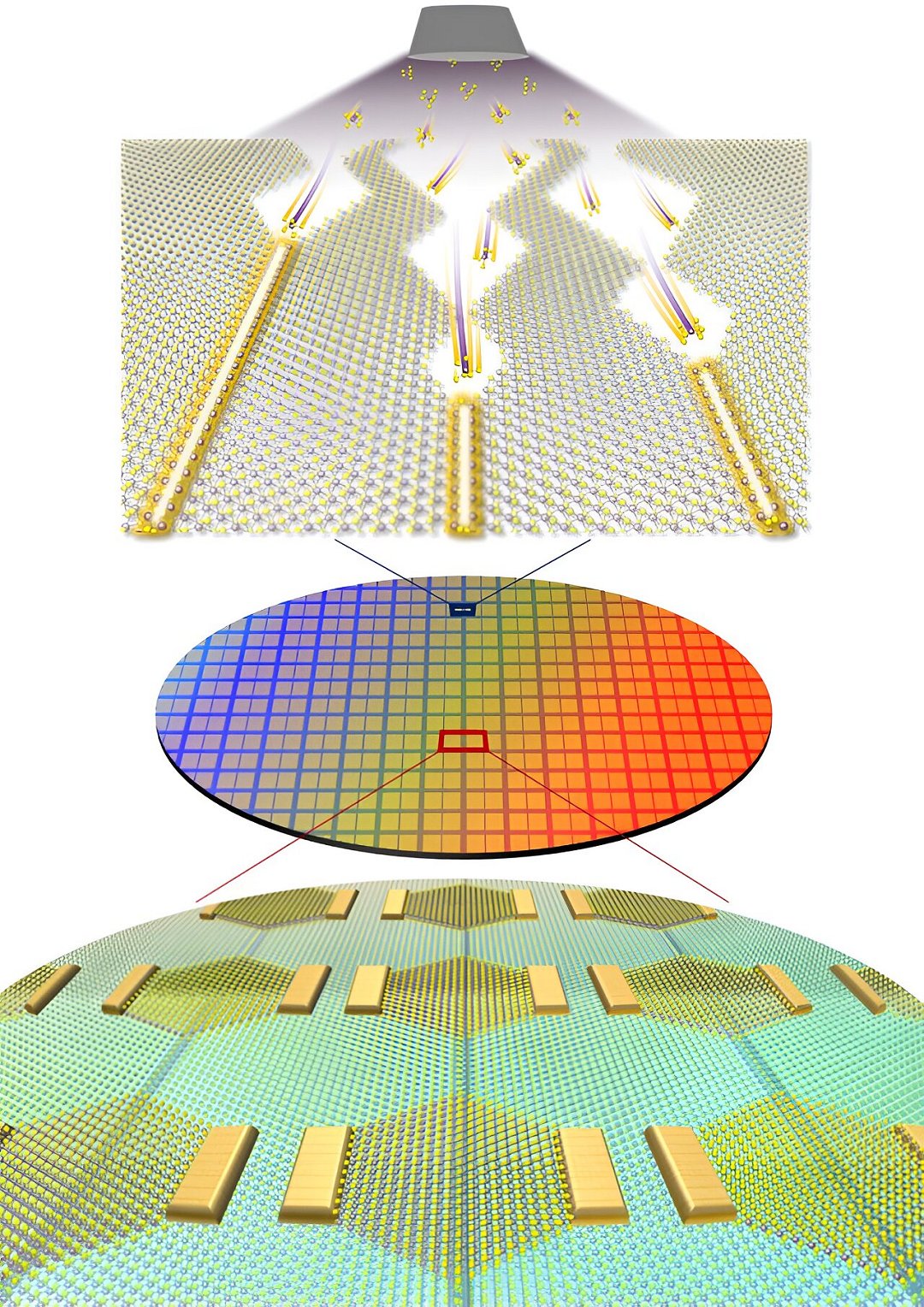

[Imagem: Institute for Basic Science]

Transistores 1D e 2D

Enquanto a TSMC (Taiwan Semiconductor Manufacturing Company), uma das maiores fabricantes de chips do mundo, anuncia com orgulho o avanço na produção de transistores de 2 nanômetros (nm), pesquisadores coreanos desenvolveram uma nova técnica que viabiliza a eletrônica sub-nanômetro.

Os chips mais avançados já em estágio comercial usam tecnologia de 3 nanômetros. Ao ficar abaixo de 1 nm, o avanço obtido agora significa que os componentes eletrônicos estão se aproximando do reino atômico - um átomo de silício tem um diâmetro de cerca de 0,23 nanômetro.

Heonsu Ahn e colegas do Instituto de Ciências Básicas, na Coreia do Sul, implementaram um novo método que consegue fazer crescimento epitaxial de materiais metálicos unidimensionais (1D, ou nanofio) com largura inferior a 1 nm. Esse processo foi então aplicado para desenvolver uma nova estrutura para circuitos lógicos usando semicondutores bidimensionais (2D) - os nanofios metálicos 1D funcionam como eletrodo de porta dos transistores 2D.

Existe um amplo esforço de desenvolvimento de semicondutores bidimensionais (2D), que apresentam excelentes propriedades mesmo no limite extremo da espessura de um material, já na escala atômica, mas esses esforços tipicamente envolvem os chamados materiais de van der Waals, como a molibdenita, os dicalcogenetos de metais de transição ou mesmo o grafeno.

Mas construir transistores ultraminiaturizados, capazes de controlar o movimento dos elétrons dentro de poucos nanômetros, ainda impõe desafios técnicos significativos, tendo rendido até agora apenas protótipos em escala de laboratório, ou mesmo ainda enfrentando questões de pesquisa fundamental, muito longe do desenvolvimento dos processos de fabricação de circuitos integrados com esses novos materiais.

A equipe coreana deixou tudo isso para trás, mostrando que é possível ir abaixo do nanômetro usando técnicas de fabricação padrão da indústria.

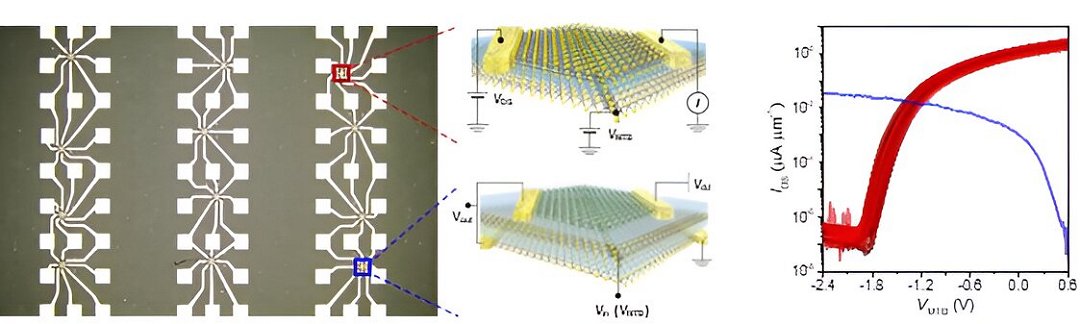

[Imagem: Institute for Basic Science]

Limite duplo espelhado

O grau de integração alcançado nos circuitos integrados é determinado pela largura e pela eficiência de controle do eletrodo de porta, que controla o fluxo de elétrons no transístor. Nos processos convencionais de fabricação de semicondutores, é impossível reduzir o comprimento da porta abaixo de alguns nanômetros devido às limitações da resolução da litografia.

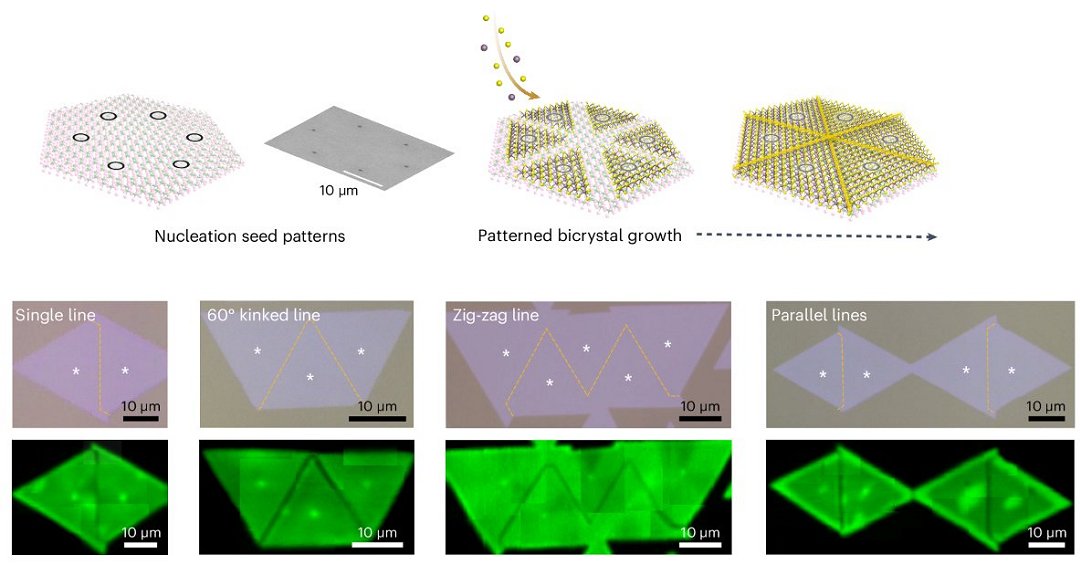

Para resolver este problema técnico, a equipe tirou proveito do fato de que a molibdenita, ou dissulfeto de molibdênio (MoS2), que é um semicondutor 2D, tem uma característica fundamental, conhecido como MTB, ou limite duplo espelhado, que é representada por um nanofio metálico 1D, com largura de apenas 0,4 nm. Esse nanofio foi então usado como um eletrodo de porta, superando as limitações do processo de litografia.

O MTB (limite duplo espelhado) de um semicondutor é um conceito fundamental na física, definido como a energia mínima necessária para excitar um elétron do topo da banda de valência, levando-o para a banda de condução, a região de energia onde os elétrons podem se mover livremente e contribuir para a condutividade elétrica.

E o processo desenvolvido pela equipe não se limitou à miniaturização de componentes individuais, sendo usado para construir circuitos eletrônicos altamente integrados e de grandes áreas.

[Imagem: Heonsu Ahn et al. - 10.1038/s41565-024-01706-1]

Além do futurístico

O avanço é mais significativo do que se imagina. Por exemplo, o Roteiro Internacional para Dispositivos e Sistemas (IRDS), do instituto norte-americano IEEE, prevê que a tecnologia de semicondutores atingirá o patamar de 0,5 nm até 2037, com transistores com 12 nm de comprimentos de porta.

O que a equipe coreana demonstrou agora é que a largura do canal modulada pelo campo elétrico aplicado a partir da porta 1D pode ser tão pequena quanto 3,9 nm, excedendo significativamente a previsão futurista daquele Roteiro.

O transístor baseado em MTB 1D também oferece vantagens no desempenho do circuito: Tecnologias como FinFET ou GAAFET, adotadas para a miniaturização dos componentes semicondutores de silício, sofrem de capacitância parasita devido às estruturas complexas que os transistores precisam assumir, gerando instabilidade em circuitos altamente integrados. Por sua vez, o transístor com porta 1D na verdade minimiza a capacitância parasita, devido à sua estrutura simples e por ser extremamente estreito.

Além disso, a obtenção da fase metálica 1D por meio do controle da estrutura cristalina do semicondutor 2D em nível atômico, representa um avanço significativo não apenas para a tecnologia de semicondutores de próxima geração, mas também para a ciência básica dos materiais, demonstrando a síntese em grande área de novas fases de materiais através do controle artificial de suas estruturas cristalinas.

"A fase metálica 1D obtida através do crescimento epitaxial é um novo processo de material que pode ser aplicado a processos semicondutores ultraminiaturizados. A expectativa é que ela se torne uma tecnologia chave para o desenvolvimento de vários componentes eletrônicos de baixo consumo e alto desempenho no futuro, disse o professor Jo Moon-Ho.

Artigo: Integrated 1D epitaxial mirror twin boundaries for ultrascaled 2D MoS2 field-effect transistors

Autores: Heonsu Ahn, Gunho Moon, Hang-gyo Jung, Bingchen Deng, Dong-Hwan Yang, Sera Yang, Cheolhee Han, Hyunje Cho, Youngki Yeo, Cheol-Joo Kim, Chan-Ho Yang, Jonghwan Kim, Si-Young Choi, Hongkun Park, Jongwook Jeon, Jin-Hong Park, Moon-Ho Jo

Revista: Nature Nanotechnology

DOI: 10.1038/s41565-024-01706-1

Humanos como hardware: Computação é feita na pele do nosso braço

Descoberta nova fase da matéria: "Meio gelo, meio fogo"

Ar-condicionado verde e de estado sólido alcança escala de quilowatts

Constantes fundamentais da natureza garantem supercondutores a temperatura ambiente

Eletricidade é gerada usando rotação da Terra em seu próprio campo magnético

Água líquida não é única: São dois líquidos diferentes

Algo do nada: Físicos resfriam objeto medindo... nada

Lançado um "linux" para computadores quânticos

Rival dos computadores quânticos tem avanço revolucionário

Energia escura não é o que pensamos, o que muda nossa visão do Universo

Vórtion: Novo estado magnético imita sinapses, guarda dados e muito mais

Memórias digitais ficam melhores graças a um gás nobre

Raízes de árvores inspiram eletrônicos flexíveis robustos

Descoberto novo fenômeno no comportamento das ondas acústicas

Efeito de proximidade faz materiais avançados ganharem novas propriedades

Estrutura fina como papel leva eletrônica flexível para uso no espaço

Todos os direitos reservados.

É proibida a reprodução total ou parcial, por qualquer meio, sem prévia autorização por escrito.