Computador probabilístico mais próximo da fabricação industrial

Redação do Site Inovação Tecnológica - 31/05/2024

[Imagem: Nihal Sanjay Singh et al. - 10.1038/s41467-024-46645-6]

Processador probabilístico

Uma equipe das universidades da Califórnia de Santa Bárbara (EUA) e Tohoku (Japão) prossegue firme em sua proposta de criar um computador probabilístico que possa ser implementado na prática.

Um computador probabilístico, ou p-computador, usa blocos de construção naturalmente aleatórios, chamados bits probabilísticos, ou p-bits. Ao contrário dos bits dos computadores tradicionais, que precisam ter valores definidos (0 ou 1), os p-bits não têm um valor específico, eles oscilam entre os valores.

Além de gastar muito menos energia, essa arquitetura é particularmente adequada para problemas como inferência e amostragem, o que significa uma capacidade inata de resolver com eficiência várias tarefas computacionalmente difíceis em aprendizado de máquina e inteligência artificial.

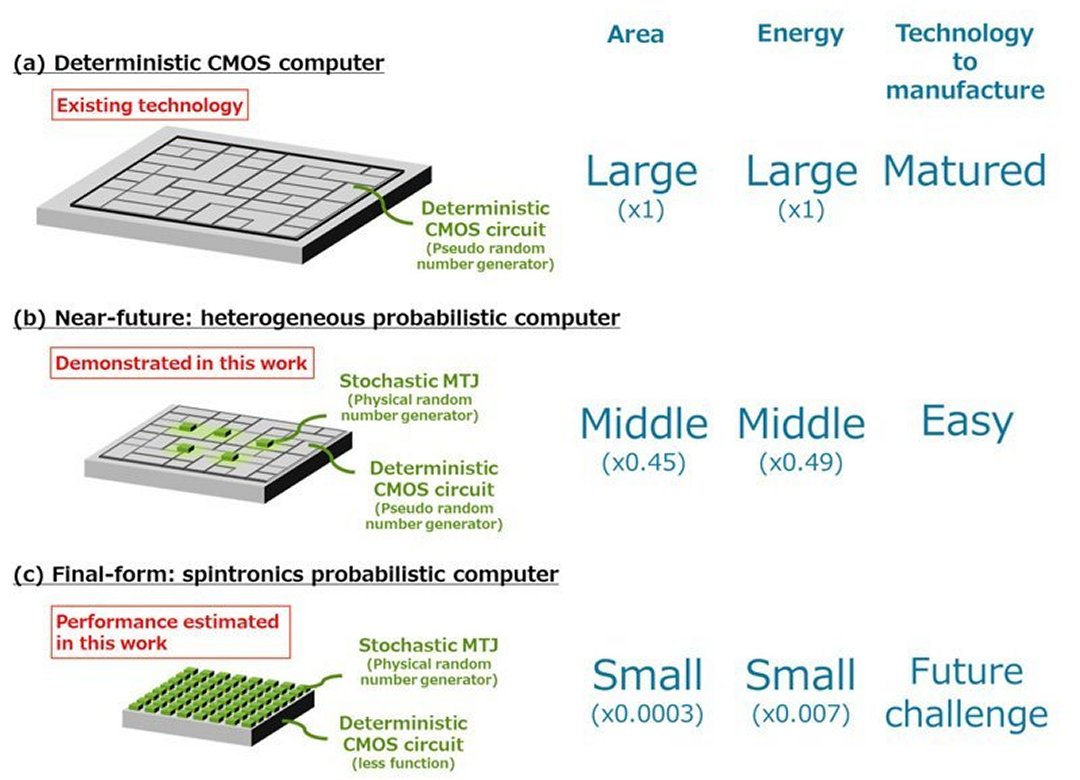

No ano passado, a equipe havia apresentado uma versão do seu p-computador usando componentes spintrônicos. Agora eles deram um passo rumo a tornar a arquitetura mais próxima de poder ser fabricada em escala industrial.

O novo protótipo combina um circuito semicondutor de óxido metálico complementar (CMOS), o padrão industrial atual, com um pequeno número de nanoímãs, criando um computador probabilístico heterogêneo. Embora ainda não estejam inseridos nas linhas de produção atuais, os nanoímãs não têm impedimentos significativos para chegar lá, só sendo necessário um bom motivo para fabricá-los em série.

[Imagem: Nihal Sanjay Singh et al. - 10.1038/s41467-024-46645-6]

Ganhos de 10.000 vezes

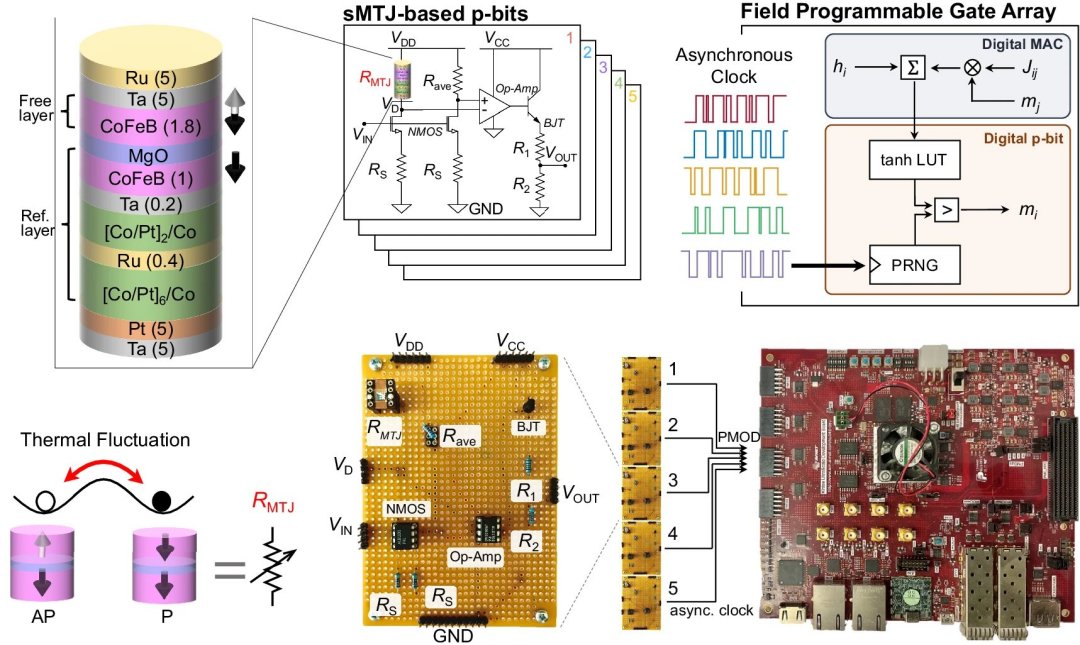

A equipe usou nanoímãs para desenvolver junções de túneis magnéticos estocásticos (sMTJs) no nível dos componentes, o que permitiu construir os p-bits mais rápidos já feitos até hoje.

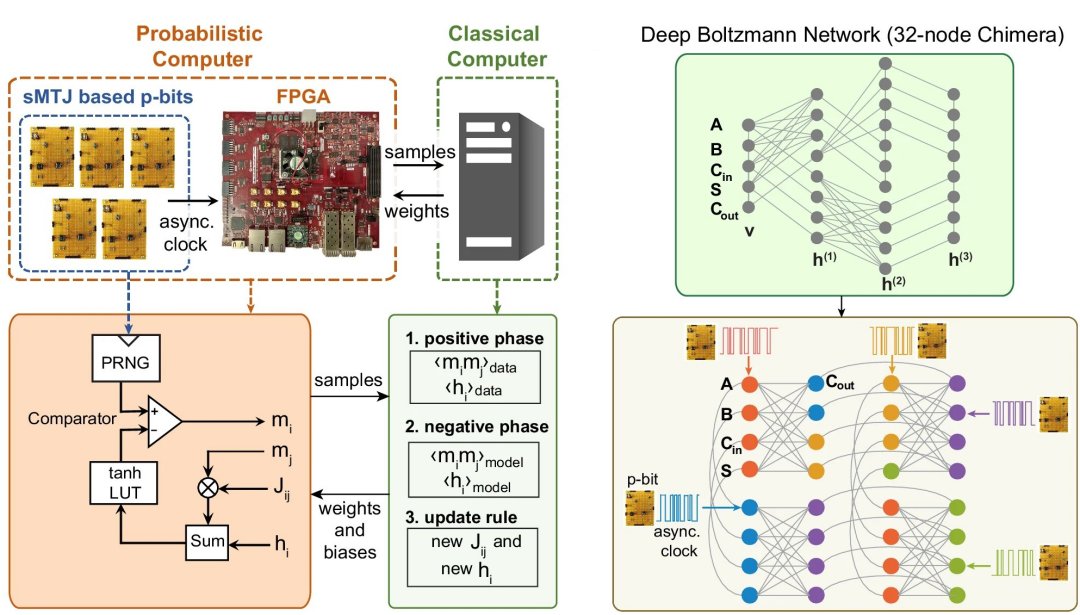

Agora, eles combinaram os bits probabilísticos sMTJs com chips programáveis comuns, conhecidos como FPGA (Field Programmable Gate Arrays) para criar um protótipo CMOS + sMTJ, que a equipe chama de "versão heterogênea de computador probabilístico para um futuro próximo", em referência ao nível de prontidão tecnológica dos seus componentes spintrônicos.

O sistema foi projetado de tal forma que os bits probabilísticos spintrônicos, que já faziam parte da versão anterior, gerem um número aleatório físico que aciona os geradores de números pseudo-aleatórios programados no circuito CMOS ou em um chip FPGA.

Os ganhos foram impressionantes: Para uma tarefa típica de inteligência artificial, o computador probabilístico alcançou uma redução de quatro ordens de magnitude (10.000 vezes) na área e uma redução de três ordens de magnitude (1.000 vezes) no consumo de energia, em comparação com os circuitos CMOS atuais. "Comparações detalhadas em nível de transístor revelam que p-bits baseados em sMTJs podem substituir até 10.000 transistores CMOS, enquanto dissipam duas ordens de magnitude menos energia," escreveu a equipe.

[Imagem: Nihal Sanjay Singh et al. - 10.1038/s41467-024-46645-6]

Futuro próximo

Não por acaso, a computação probabilística é considerada uma ponte para a computação quântica, mas com a grande vantagem de que tudo já funciona à temperatura ambiente.

"Nosso protótipo demonstrou que se pode alcançar um excelente desempenho computacional acionando geradores de números pseudo-aleatórios em um circuito CMOS determinístico, com números aleatórios físicos gerados por um número limitado de nanomagnetos estocásticos," detalhou o professor Shunsuke Fukami. "Especificamente falando, um número limitado de bits probabilísticos (p-bits) com uma junção de túnel magnético estocástico (s-MTJ) deve ser fabricado com uma tecnologia de integração em um futuro próximo."

Artigo: CMOS plus stochastic nanomagnets enabling heterogeneous computers for probabilistic inference and learning

Autores: Nihal Sanjay Singh, Keito Kobayashi, Qixuan Cao, Kemal Selcuk, Tianrui Hu, Shaila Niazi, Navid Anjum Aadit, Shun Kanai, Hideo Ohno, Shunsuke Fukami, Kerem Y. Camsari

Revista: Nature Communications

Vol.: 15, Article number: 2685

DOI: 10.1038/s41467-024-46645-6

Superfluidez em supersólido é confirmada por vórtices quânticos

Captura de água da umidade do ar agora até em regiões áridas

Hidrogéis fazem fotossíntese artificial para produzir hidrogênio solar

Gato de Schrodinger recordista fica indeciso entre vivo ou morto por 23s

"Monstros Vermelhas": Webb descobre mais três galáxias que contestam teorias

Cadeias de qubits que conversam entre si são criadas no grafeno

Desvendado segredo de Urano: Foi só uma coincidência

Reator torna captura direta de CO2 mais eficiente e mais flexível

Será que a teoria de Einstein só vale na escala do Sistema Solar?

Pela primeira vez fotografamos uma estrela de outra galáxia

Coprocessador metatrônico resolve equações na velocidade da luz

RRAMs, as memórias que fazem cálculos, mais próximas de mudar a computação

Memória de luz traz avanço multinível para computação óptica

Hardware magnético junta duas arquiteturas de computação alternativa

Corrente alternada faz computação magnética super eficiente

Nobel de Física premia inteligência artificial

Todos os direitos reservados.

É proibida a reprodução total ou parcial, por qualquer meio, sem prévia autorização por escrito.