Chips ficam 50% menores com capacitores enfiados em camada intermediária

Redação do Site Inovação Tecnológica - 14/06/2021

[Imagem: Yi-Chieh Tsai et al. - 10.1109/TED.2021.3082497]

Miniaturização

Engenheiros japoneses descobriram como usar uma camada "inerte" dentro dos processadores para colocar componentes ativos.

Esse melhor aproveitamento da área permitiu um nível de compactação e miniaturização impressionante, além de reduzir as fiações no interior do próprio chip.

A técnica consiste em construir um componente eletrônico chamado capacitor dentro de uma camada conhecida como "interposer", que funciona como um espaçador, isolante e guia de conexões entre os transistores e a fiação do chip.

Yi-Chieh Tsai e colegas do Instituto de Tecnologia de Tóquio demonstraram que as camadas intermediárias de silício podem ser transformadas em capacitores funcionais, economizando um espaço considerável e trazendo vários outros benefícios.

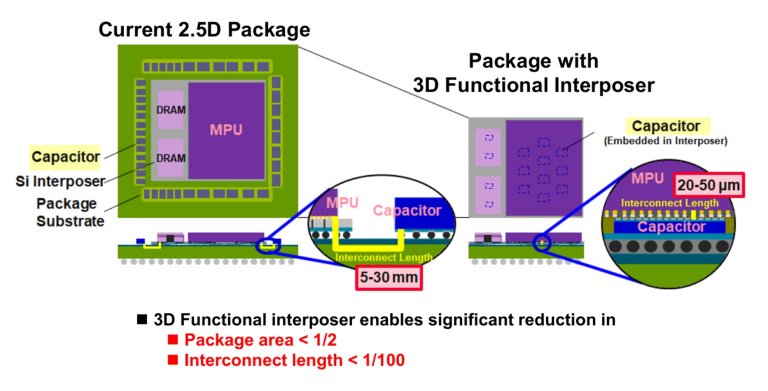

Nos chips mais modernos, incluindo as DRAMs e os processadores, esses interposers funcionam como túneis condutores verticais, que unem as conexões nos chips com saliências de solda no substrato da embalagem. Os capacitores são colocados nesse substrato, próximo aos componentes aos quais servem, o que exige uma conexão de 5 a 30 mm entre seus terminais e os do chip.

A nova proposta é que a própria camada de silício funcione como capacitor.

A equipe conseguiu isso por meio de um novo processo de fabricação no qual os capacitores são incorporados dentro de uma peça de silício de 300 mm usando resina e cola. As interconexões entre o chip e o capacitor são feitas diretamente com vias passantes de silício, sem a necessidade de saliências de solda.

"Nosso interposer funcional 3D, sem saliências [as protuberâncias das soldas], permite uma redução notável na área do pacote de cerca de 50% e um comprimento de interconexão cem vezes menor," comentou o professor Takayuki Ohba.

Artigo: Electrical Characteristics and Reliability of Wafer-on-Wafer (WOW) Bumpless Through-Silicon Via

Autores: Yi-Chieh Tsai, Chia-Hsuan Lee, Hsin-Chi Chang, Jui-Han Liu, Han-Wen Hu, Hiroyuki Ito, Young Suk Kim, Takayuki Ohba, Kuan-Neng Chen

Revista: Proceedings of the IEEE Electronic Components and Technology Conference

Vol.: 99:1-6

DOI: 10.1109/TED.2021.3082497

Ar-condicionado verde e de estado sólido alcança escala de quilowatts

Constantes fundamentais da natureza garantem supercondutores a temperatura ambiente

Água líquida não é única: São dois líquidos diferentes

Algo do nada: Físicos resfriam objeto medindo... nada

Eletricidade é gerada usando rotação da Terra em seu próprio campo magnético

Lançado um "linux" para computadores quânticos

Medição que contesta teoria da física é revalidada

Energia escura não é o que pensamos, o que muda nossa visão do Universo

Rival dos computadores quânticos tem avanço revolucionário

Lançado computador quântico de silício pronto para ser plugado na tomada

Metais 2D: Pela primeira vez, metais viram folhas com átomos de espessura

Relógios atômicos de pulso revolucionarão celulares, GPS e mais

Criado aparelho na fronteira entre a física clássica e a física quântica

Miniaturizado gerador de fótons entrelaçados para tecnologias quânticas

Diamante é fabricado na forma de película ultraflexível

Lente plana amplia horizontes tecnológicos, com foco na miniaturização

Todos os direitos reservados.

É proibida a reprodução total ou parcial, por qualquer meio, sem prévia autorização por escrito.